공정 압축으로 원가 경쟁력 확보

|

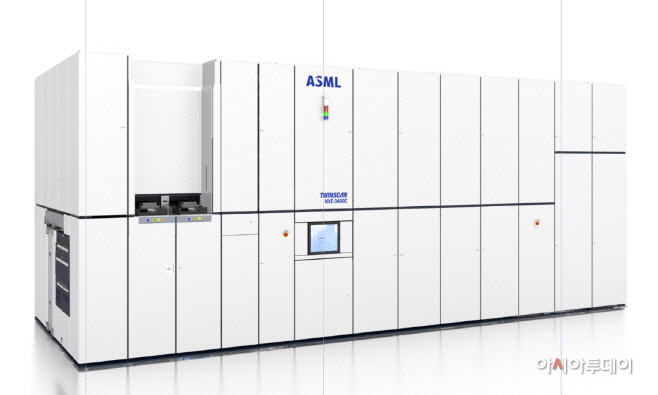

2일 반도체 업계에 따르면 삼성전자가 EUV 기술을 D램 생산에 적용하는데 필요한 마스크 보호막(페리클) 개발이 막바지에 접어든 것으로 전해진다. SK하이닉스, 마이크론, 난야 등 D램 경쟁사들보다 빠른 개발 속도다.

페리클은 쉽게 표현하면 반도체 회로 모양을 본딴 마스크에 붙이는 보호 필름이다. 반도체 회사는 웨이퍼에 원하는 회로를 새기기 위해 회로 모양을 본 딴 마스크를 만든다. 마스크는 EUV 광선이 통과하는 판화의 틀 같은 역할이다. EUV 광선을 마스크에 쏘면 촘촘히 새겨진 미세한 구멍대로 웨이퍼에 회로가 그려진다. ‘마스크로 웨이퍼에 회로를 찍어낸다’고 표현하는 바로 그 공정이다. 웨이퍼에 회로를 찍어내는 중대한 과정인 만큼 마스크는 절대 오염돼선 안 된다. 마스크가 오염됐다간 작업한 웨이퍼를 모조리 버려야 한다.

기존에 쓰던 이머전 장비용 마스크는 페리클이 있어, 마스크가 오염되도 다시 쓸 수 있었다. 페리클만 교체하면 되기 때문이다. 하지만 EUV 장비용 마스크를 보호하는 페리클은 아직 없었다. EUV 장비로 D램을 생산하다가 마스크 오염이 감지되면 폐기했어야 했다. 반도체 업계 한 관계자는 “페리클 외에도 EUV 장비의 D램 양산 적용을 위해 새롭게 개발하고 해결해야 할 난제가 수두룩한 상황”이라며 “EUV 장비만 산다고 다 되는게 아니라는 의미”라고 전했다.

삼성전자가 2018년부터 EUV 장비 도입을 추진하겠다고 밝혔지만, 올해 하반기에야 ‘14나노 D램’ 양산에 EUV 기술을 적용하는 것도 이 때문이다. 한진만 메모리사업부 부사장은 “EUV는 단순히 설비를 구매해 생산에 적용하는 것보다 마스크, 검사와 에코시스템 구축하고 관련 노하우를 쌓아서 기술을 끌어올리는 것이 중요하다”고 설명했다.

삼성전자는 페리클 개발 완료 시점인 올해 하반기부터 14나노 D램을 생산할 때 다섯 레이어에 EUV를 적용할 계획이다. 기존 공정대로라면 5개의 마스크를 만들어 웨이퍼에 회로를 그렸어야 하는데, EUV로 한 개의 마스크만 사용해 회로를 그렸다는 의미다. 5개 만들던 마스크를 1개만 만들었고, 공정이 압축됐으니 원가 경쟁력은 더 높아진다.

|

다만 SK하이닉스가 EUV 공정을 완성했다는 입장은 아니다. SK하이닉스 관계자는 “4세대 D램 생산에 EUV 기술을 썼지만 본격 적용 전 테스트 성격이 강하다”며 “우리는 기존 이머전 장비와 EUV 장비 활용 그 중간에 와있다”고 설명했다. 또 “EUV 장비를 처음 도입하는 만큼 우리가 예상하지 못했던 여러 어려움이 예상된다. 어떤 업체가 빨리 극복하느냐가 D램 업체의 경쟁력을 결정 짓는 관건이 될 것 같다”고 덧붙였다.

한편 페리클은 삼성전자가 지분투자한 에프에스티가 생산한다. 에프에스티는 국내 최대 반도체용 페리클(ArF·KrF) 제조사다. 에프에스티는 삼성전자에 공급할 폴리실리콘카바이드 소재의 EUV 페리클 개발에 집중해왔다.